| 入手先 |

|

http://www.inf.pucrs.br/~moraes/topicos/hdls/HANDEL-C/

のPC_BINの下にあるHCC.EXE。ドキュメント類も落としておくと良いだろう

|

| インストール |

|

特別なことは必要ない。とりあえずパスがとおっていればいい模様

ただし、なぜかWindowsXPのDOS窓ではうまくいかない。Win98/2000のDOS窓は大丈夫

|

| はじめてのサンプル |

|

とりあえず作ったのは下に書いたようなこんなソース。HCCはXNFを生成するのがデフォルトだけども、今のツールではXNFは受け付けない。

ここで、fpga_typeにVHDLを指定すると、VHDLソースコードを生成する。fpga_chipなどはこの際特に意味はない。

こいつをdefault.hccという名前でこしらえておく。

const spec t1 = {

fpga_type = "VHDL", // これでVHDL出力を指示

fpga_chip = "3195APQ160-3", //

てきとー

clock_pad = "P160", //いいかげん

not_error_pad = "P55", //なんだそれ?

finish_pad = "P44", //しらない

clock_divider = "1", //意味あるのか?

carry_weight = "50", //なんじゃらほい

critical_weight = "100" //あとは野となれ

};

const spec uudat = { // こんな感じでポートが定義できる模様

data = {"P0","P1","P3","P4"}, //

これが実体

txrdy = "pt", // 一応txrdyは勝手に生成されてしまうので、その分の定義

rxrdy = "pr" // こっちは要らないかも

};

//=====おまじないはここまで=======

//=====ここから本体 =======

//== main()の引数が一般的なC言語と違っているのは

//== この時代のHandel-Cでは引数で

//== ポートやらチップ種別なんかを宣言する

//== という方法を使っていたため。

//== 今のバージョンではinterfaceなどに切り替わって

//== main()の引数はvoidになった

main(target = t1,port (out) pport = uudat:4)

{

int x:8;

x=0;

do {

x = x+1;

pport ! x.(0..3); //この時代のポートへの出力は「チャンネル」

//扱いで出力するしかなさそう

} while (1);

}

|

| コンパイル |

|

hCC -ns ソースファイル名

でいい。-nsはシミュレーションしないよという指定。なぜかコンパイルが終わると即シミュレーションを実行しようとするので、黙らせておくためにこうした。

|

| VHDLソースコード修正 |

|

このままQUARTUSにかけてみたら出るわ出るわのエラーの嵐。

どうもいかんのだなということで手作業で修正した。

今のところ

・使ってないからコメントアウトしてしまうもの

・出力ポートを直接リードしようとするので一回signalで受けてからポートに出すように記述変更

といったもの。

修正したソースはこんな感じ

|

| ライブラリの作成 |

|

ANDだとかORだとかを直接落とさずにコンポーネントとして使おうとするのだけども、これがどこにも見当たらない。仕方がないので、名前から想像しながら作成したライブラリがこれ。

ただし、今のところ上で示したサンプルが動くのに必要な分しか作っていないので、今後もっと拡充しなくてはならないかもしれない。

|

| フィッティング |

|

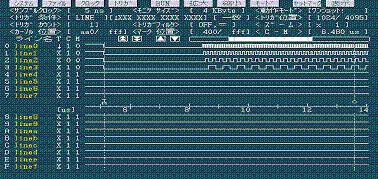

これでVHDLのソースが出来上がったので、これをQUARTUSに与えて、実際のFPGA(私が使ったのはSTRATIXボード)にマッピングしてみたらとりあえず動くところまでいった。

この結果が上に示した波形。

ソースコードではxをインクリメントしながら下位4ビットをpportに出力しているのだが、確かに波形として現れているのがみてとれる。

|